- 非IC关键词

深圳市誉鼎科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

http://www.dzsc.com/company/1016738/index.html

收藏本公司 人气:61401

企业认证

- 现货认证

企业档案

- 相关证件:

- 会员类型:

- 会员年限:3年

- 阿库IM:

- 地址:深圳市福田区华强北路华强广场A座15J

- 传真:0755-83232905

- E-mail:932441002@qq.com

您的当前位置:深圳市誉鼎科技有限公司 > 元器件产品

相关产品

产品信息

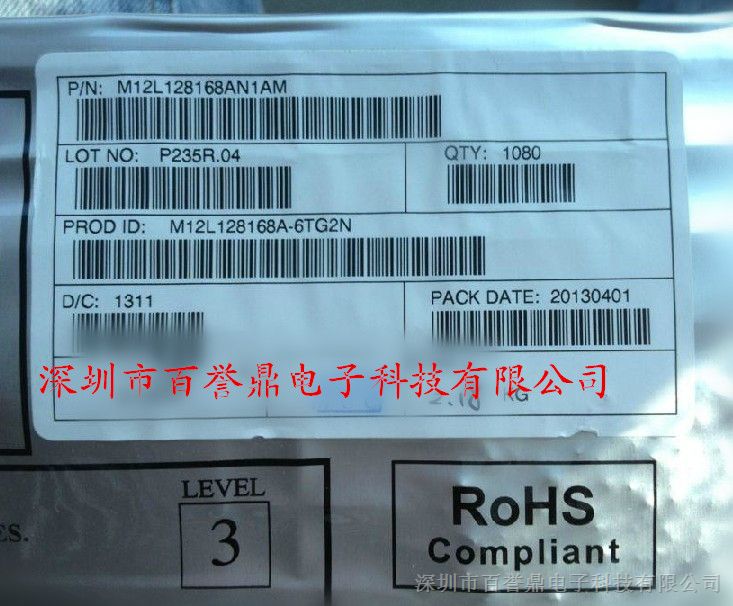

ESMT M12L128168A (2L)

Elite Semiconductor Memory Technology Inc. Publication Date: Jun. 2012

Revision: 1.3 1/45

SDRAM 2M x 16 Bit x 4 Banks

Synchronous DRAM

FEATURES

y JEDEC standard 3.3V power supply

y LVTTL compatible with multiplexed address

y Four banks operation

y MRS cycle with address key programs

- CAS Latency ( 2 & 3 )

- Burst Length ( 1, 2, 4, 8 & full page )

- Burst Type ( Sequential & Interleave )

y All inputs are sampled at the positive going edge of the

system clock

y Burst Read single write operation

y DQM for masking

y Auto & self refresh

y 64ms refresh period (4K cycle)

ORDERING INFORMATION

Product ID Max Freq. Package Comments

M12L128168A-5TG2L 200MHz 54 Pin TSOP II Pb-free

M12L128168A-5BG2L 200MHz 54 Ball FBGA Pb-free

M12L128168A-6TG2L 166MHz 54 Pin TSOP II Pb-free

M12L128168A-6BG2L 166MHz 54 Ball FBGA Pb-free

M12L128168A-7TG2L 143MHz 54 Pin TSOP II Pb-free

M12L128168A-7BG2L 143MHz 54 Ball FBGA Pb-free

GENERAL DESCRIPTION

The M12L128168A is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 16 bits.

Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle.

Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a

variety of high bandwidth, high performance memory system applications.

Elite Semiconductor Memory Technology Inc. Publication Date: Jun. 2012

Revision: 1.3 1/45

SDRAM 2M x 16 Bit x 4 Banks

Synchronous DRAM

FEATURES

y JEDEC standard 3.3V power supply

y LVTTL compatible with multiplexed address

y Four banks operation

y MRS cycle with address key programs

- CAS Latency ( 2 & 3 )

- Burst Length ( 1, 2, 4, 8 & full page )

- Burst Type ( Sequential & Interleave )

y All inputs are sampled at the positive going edge of the

system clock

y Burst Read single write operation

y DQM for masking

y Auto & self refresh

y 64ms refresh period (4K cycle)

ORDERING INFORMATION

Product ID Max Freq. Package Comments

M12L128168A-5TG2L 200MHz 54 Pin TSOP II Pb-free

M12L128168A-5BG2L 200MHz 54 Ball FBGA Pb-free

M12L128168A-6TG2L 166MHz 54 Pin TSOP II Pb-free

M12L128168A-6BG2L 166MHz 54 Ball FBGA Pb-free

M12L128168A-7TG2L 143MHz 54 Pin TSOP II Pb-free

M12L128168A-7BG2L 143MHz 54 Ball FBGA Pb-free

GENERAL DESCRIPTION

The M12L128168A is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 16 bits.

Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle.

Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a

variety of high bandwidth, high performance memory system applications.

询价

询价